#### **Cooperation Agreement for Small Form Factor Transceivers**

Agilent Technologies, E2O Communications, Fujikura Technology America Corp, IBM Corp., Lucent Technologies Inc., Molex Inc., Sumitomo Electric Lightwave Corp., Tyco Electronics Inc.

#### I. Purpose of the Cooperation Agreement

Each party desires to establish internationally compatible sources of a fiber optic transceiver module in support of standards for fiber optic systems including Asynchronous Transfer Mode (ATM), FDDI, Fibre Channel, Fast Ethernet and Gigabit Ethernet, and Synchronous Optical Network (SONET)/Synchronous Digital Hierarchy (SDH) applications. Each party further desires to establish uniformity in the industry for the Transceiver "Package Outline", "Circuit Board Layout" and "Pin Function Definitions" described in Appendix A. Each party expects that the establishment of compatible sources for an interchangeable transceiver module will allow the entire fiber optic marketplace to grow more rapidly. This enhanced growth, providing more customer choice and vigorous competition are the express purposes of the Agreement. The parties desire to establish compatible sources for additional products in the future.

#### **II. Agreement**

#### A. General

The parties agree to cooperate by supporting common product interface specifications for fiber optic transceivers with the package "Package Outline", "Circuit Board Layout" and "Pin Function Definitions" described here and in Appendix A. Initial products utilizing this agreement may include Fiber Optic Transceivers at 100 to 2.5 Gb/s for multimode and single mode fiber applications. Other fiber optic transceivers may follow as needed in the marketplace. The mechanical dimensions shall be compatible with the package "Package Outline", "Circuit Board Layout" and "Pin Function Definitions" as shown in Appendix A. The overall package dimensions shall not exceed the maximum indicated dimensions, and the pins and mounting posts shall be located such that the products are mechanically interchangeable in a circuit board. The electrical and optical specifications shall be compatible with those enumerated in the appropriate standards (i.e., the IEEE 802.3z Gigabit Ethernet standard and the ITU G.957 Synchronous Digital Hierarchy standard). In addition, the parties may work together to recommend circuit layouts for electrical input and output terminations, and grounding practices. The transceivers per this agreement will accept an optical connector such as the duplex LC, MT-RJ or the SC/DC connector. This agreement does not preclude any of the parties from offering Small Form Factor transceivers for other connectors and vice-versa. Internal design of the product is entirely at the discretion of each party and is not covered by this Agreement. The parties recognize that their products may not be identical, but need only meet the above criteria.

#### B. Licensing and Fees

No license is granted under the patents, know-how, tradesecrets or any other technology of any party to this agreement either expressly or by implication or by estoppel. Each party is free to seek technology or other exchanges with other firms in order to support its activities under this Agreement.

#### C. Scope of the Agreement

The scope of this Agreement includes transceiver modules for transmission rates from 100 to 2.5 Gb/s operating over multimode and single mode fiber. Each party agrees to be responsible for its own development, manufacturing, marketing, and selling in order to supply transceiver modules meeting the attached interface specifications. This Agreement does not preclude any party from offering other products which may not meet the attached interface specifications. Each party retains complete liberty regarding its methods of implementing a supply of product, e.g. by engineering effort or by technology licensing or transfer or combination of these or other practices. Each party also retains sole discretion in its choice of sales channels and distribution. Each party affirms its intention to freely and openly compete in the marketplace with the parties as well as other competitors. Each party expects to support products meeting the attached specifications for as long as marketplace conditions warrant. No specific time limit is associated with this Agreement. The determination of marketplace condition suitability is to be made by each party individually and in each party's sole discretion.

#### **III. Public Announcement**

#### A. Announcing the Agreement

Each party agrees to announce this Agreement in a manner agreed upon by the parties. These announcements will mention all the parties who have signed this agreement. Each party agrees to seek public attention by means of such an announcement. Each party agrees to contribute time and effort of its sole discretion toward preparing and making such an announcement.

#### B. Promotion of the Agreement

After the Agreement is announced, each party may advertise or otherwise promote this Agreement in any way it deems appropriate. Mutual consent of any other party is required if such other party is to be mentioned by name.

## **IV. Other Vendors**

#### A. Other Vendors Matching the Product Configuration

The parties recognize that additional vendors may choose to match the attached product specifications after this Agreement is announced. Each party recognizes it is desirable and keeping with the intent of the Agreement for such additional vendors to support the transceiver mechanical dimensions and interface attributes described in Appendix A. Therefore, each party agrees to encourage other vendors to support these product specifications.

#### **B.** Naming Other Vendors

Each party agrees to have written internal procedures that require such party to name the other parties when customers ask who intends to be a source for the transceivers described in this Agreement. Each party agrees for such procedures to require it to name the others regardless as to whether another of the parties has already supplied similar transceiver module products to that customer. An example of suggested wording is; "Agilent, E2O, FTAC, IBM, Lucent, Molex, Sumitomo, and Tyco have signed a Cooperation Agreement relating to the establishment of Small Form Factor transceivers for multimode and single mode fiber operating in the range of 100 to 2.5 Gb/s data rates." The parties are not obligated to provide any information other than the identities of the other parties. The requirements of this provision are met entirely if a party has the aforementioned written procedures and they are made available to its sales force in the same way as are other sales related procedures.

#### **V. Future Direction**

#### A. Current Product

Should the parties agree to further explore technical and other exchanges pertaining to the products described in this Agreement, then this shall be under a separate agreement.

#### B. Withdrawal

The parties recognize that at some future time it may become less feasible to offer the products envisioned by this Agreement. A party may withdraw from its commitment to cooperate at its own discretion upon a 90-day notice to the other parties. This notice is necessary to allow the other parties to discontinue mentioning the withdrawing party as a participant in this Cooperation Agreement and to reconsider any jointly planned promotional activities.

#### **VI. Agreement Signatures**

#### A. for Agilent Technologies by:

| Signed |      |      |  |

|--------|------|------|--|

| Name   |      |      |  |

| Title  | <br> | <br> |  |

| Date   |      |      |  |

#### B. for E2O Communications by:

Signed

Name

Title

Date

#### C. for Fujikura Technology America Corp by:

| Signed | <br> | <br> | <br> |

|--------|------|------|------|

| Name   |      |      |      |

| Title  |      |      |      |

| Date   | <br> | <br> | <br> |

#### D. for IBM Corp by:

| Signed |      | <br> |      |

|--------|------|------|------|

| Name   | <br> | <br> | <br> |

| Title  | <br> | <br> | <br> |

| Date   |      |      |      |

#### E. for Lucent Technologies by:

| Signed |  |  |  |

|--------|--|--|--|

| Name   |  |  |  |

| Title  |  |  |  |

| Date   |  |  |  |

#### F. for Molex Inc. by:

Signed

Name

Title

Date

#### G. for Sumitomo by:

Signed

Name

Title

Date

#### H. for Tyco Electronics by:

| Signed |  |  |  |

|--------|--|--|--|

|        |  |  |  |

| Name   |  |  |  |

|        |  |  |  |

| Title  |  |  |  |

|        |  |  |  |

| Date   |  |  |  |

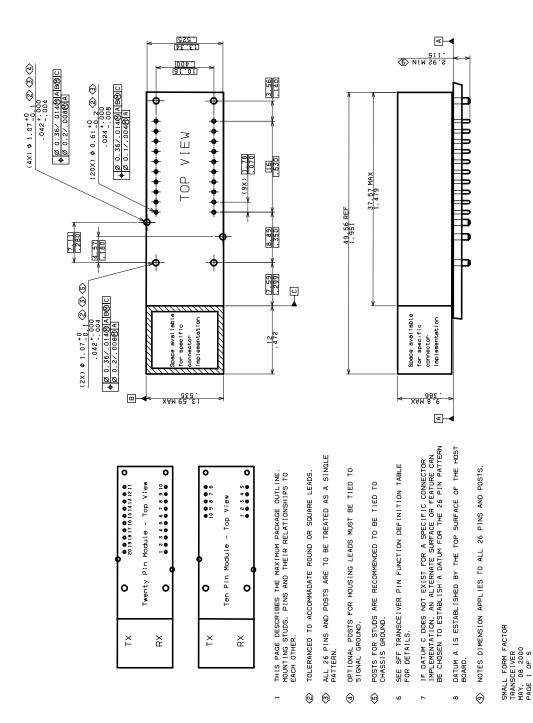

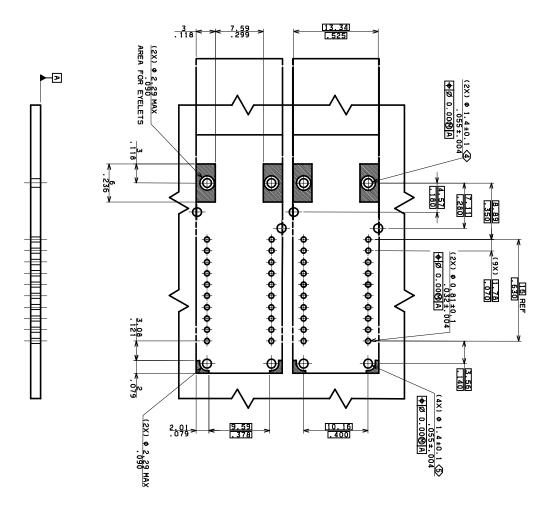

### Appendix A.1.2 Circuit Board Layout Package Outline

- 1 THIS PAGE DESCRIBES THE RECOMMENDED CIRUIT BOARD LAYOUT FOR THE SFF TRANSCEIVER.

- 2 THE HATCHED AREAS ARE KEEP-OUT AREAS RESERVED FOR HOUSING STANDOFFS. NO METAL TRACES OF GROUND CONNECTION IN KEEPOUT AREA.

- 3 20 PIN MODULE SHOWN. 10 PIN MODULE REQUIRES ONLY 16 PCB HOLES.

- (4) HOLES FOR MOUNTING STUDS MUST BE TIED TO CHASSIS GROUND.

- ⟨5⟩ HOLES FOR HOUSING LEADS MUST BE TIED TO SIGNAL GROUND.

SMALL FORM FACTOR TRANSCEIVER MAY. 08 2000 PAGE 2 OF 5

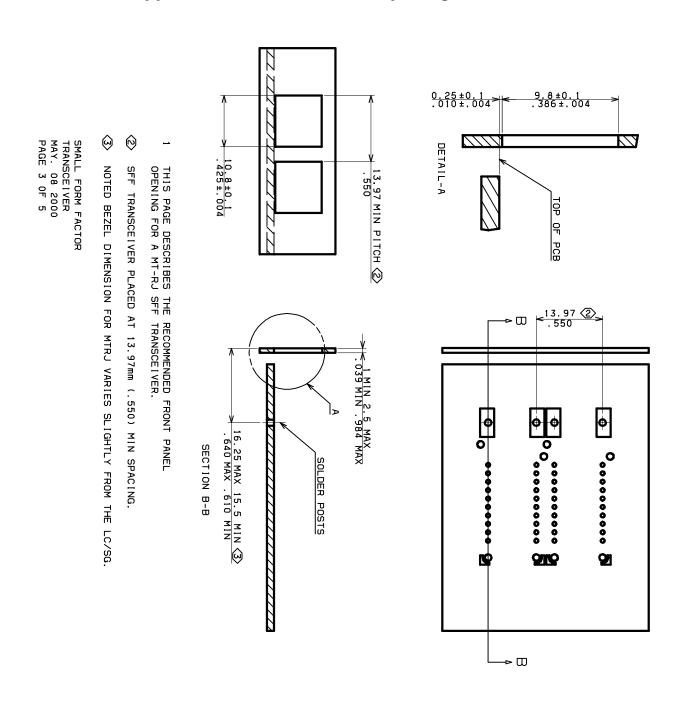

# <u>Small Form Factor Transceiver Multisource Agreement</u> Appendix A.1.3 Front Panel Opening for MT-RJ

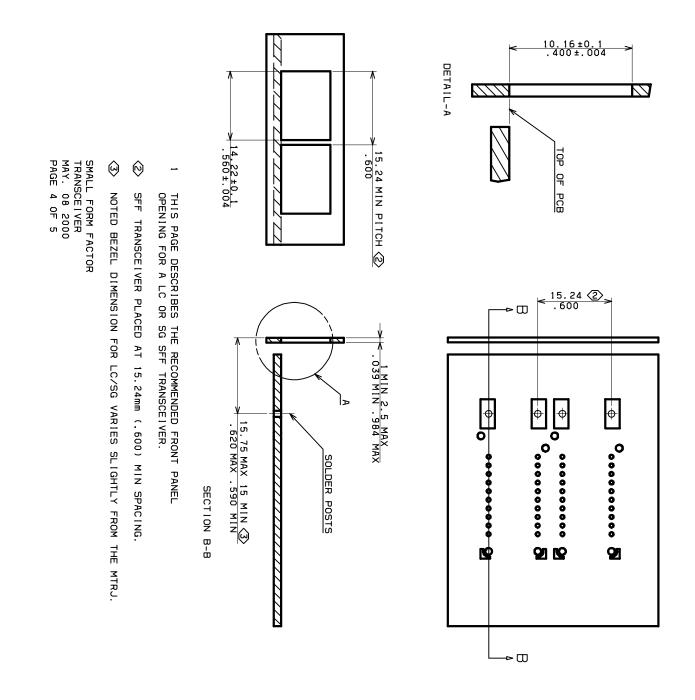

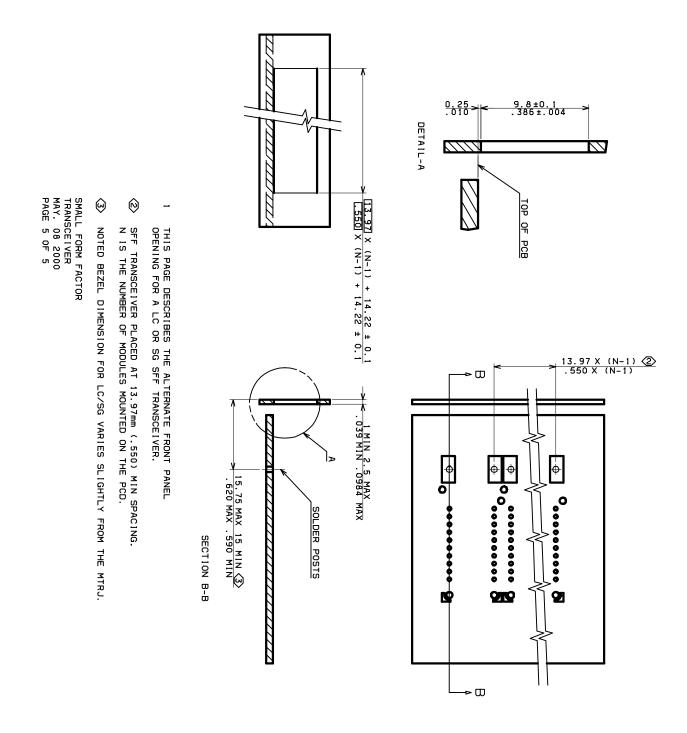

## Appendix A.1.4 Recommended Front Panel Opening for LC or SG

## Appendix A.1.5 Alternate Front Panel Opening for LC or SG

# Appendix A.2.1 Transceiver Receiver Pin Function Definition

|             | a <b>Part Versions</b><br>Dutline Drawing f<br>kage) | or Pin Positions        | where the extra featu                                                                      | transceiver are intended. The 10 pin version is intended for<br>ires of the 20 pin version are not required. The 20 pin vers<br>ond data in and out such as recovered clock and laser trans                             | ion provides extra                               |

|-------------|------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 10 Pin Part | 20 Pin Part                                          | Symbol                  | Notes                                                                                      | <b>Functional Description</b>                                                                                                                                                                                           | Logic Family                                     |

| MS          | MS                                                   | MS                      | The holes in the<br>circuit board must<br>be tied to chassis<br>ground.                    | Mounting Studs<br>The mounting studs are provided for transceiver<br>mechanical attachment to circuit board. They may<br>also provide an optional connection of the<br>transceiver to the equipment chassis ground.     | NA                                               |

| HL          | HL                                                   | HL                      | The holes in the<br>circuit board must<br>be included and be<br>tied to signal<br>ground.  | Housing Leads<br>The optional transceiver housing leads may be<br>provided for additional signal grounding. These<br>additional grounds may improve signal integrity,<br>EMC, or ESD performance.                       | NA                                               |

| No Pin      | 1                                                    | Photo-<br>detector Bias | This hole in the<br>circuit board must<br>be tied to the most<br>positive power<br>supply. | Photodetector Bias: Optional Feature<br>This lead supplies bias for the PIN photdetector<br>diode when provided as a feature of a transceiver.                                                                          | NA                                               |

| No Pin      | 2                                                    | Veer                    |                                                                                            | Receiver Signal Ground                                                                                                                                                                                                  | NA                                               |

| No Pin      | 3                                                    | Vee <sub>r</sub>        |                                                                                            | Receiver Signal Ground                                                                                                                                                                                                  | NA                                               |

| No Pin      | 4                                                    | Clk-                    | If feature is not<br>used, do not<br>connect.                                              | Received Recover Clock Out Bar:<br>Optional Feature The rising edge occurs at the rising<br>edge of the Received Data output. The falling edge<br>occurs in the middle of the Received Data baud<br>period.             | PECL                                             |

| No Pin      | 5                                                    | Clk+                    | If feature is not<br>used, do not<br>connect.                                              | Received Recover Clock Out Optional Feature The<br>falling edge occurs at the rising edge of the<br>Received Data output. The rising edge occurs in the<br>middle of the Received Data baud period                      | PECL                                             |

| 1           | 6                                                    | Vee <sub>r</sub>        |                                                                                            | Receiver Signal Ground                                                                                                                                                                                                  | NA                                               |

| 2           | 7                                                    | Vcc <sub>r</sub>        |                                                                                            | Receiver Power Supply                                                                                                                                                                                                   | NA                                               |

| 3           | 8                                                    | SD                      |                                                                                            | Signal Detect<br>Normal Operation: Logic "1" Output<br>Fault Condition: Logic"0" Output<br>This signal will be TTL for all Gb/s transceivers. For<br>Legacy applications (622 Mb/s and below), PECL<br>will be provided | TTL is preferred,<br>but PECL may be<br>provided |

| 4           | 9                                                    | RD-                     |                                                                                            | Received Data Out Bar<br>No internal terminations will be provided                                                                                                                                                      | PECL                                             |

| 5           | 10                                                   | RD+                     |                                                                                            | Received Data Out<br>No internal terminations will be provided                                                                                                                                                          | PECL                                             |

# Appendix A.2.2 Transceiver Transmitter Pin Function Definition

| (See Package       | <b>Part Versions</b><br>Outline Drawing<br>in the Package) | for Pin          | where the extra feat                                                                      | s transceiver are intended. The 10 pin version is intended for<br>ures of the 20 pin version are not required. The 20 pin vers<br>yound data in and out such as recovered clock and laser trans                                                                                                                                                                                                                            | ion provides extra |

|--------------------|------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                    |                                                            |                  | and alarms                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

| <u>10 Pin Part</u> | 20 Pin Part                                                | Symbol           | Notes                                                                                     | <b>Functional Description</b>                                                                                                                                                                                                                                                                                                                                                                                              | Logic Family       |

| MS                 | MS                                                         | MS               | The holes in the<br>circuit board must<br>be tied to chassis<br>ground.                   | Mounting Studs<br>The mounting studs are provided for transceiver<br>mechanical attachment to circuit board. They may<br>also provide an optional connection of the<br>transceiver to the equipment chassis ground.                                                                                                                                                                                                        | NA                 |

| HL                 | HL                                                         | HL               | The holes in the<br>circuit board must<br>be included and be<br>tied to signal<br>ground. | Housing Leads<br>The optional transceiver housing leads may be<br>provided for additional signal grounding. These<br>additional grounds may improve signal integrity,<br>EMC, or ESD performance.                                                                                                                                                                                                                          | NA                 |

| 6                  | 11                                                         | Vcct             |                                                                                           | Transmitter Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                  | NA                 |

| 7                  | 12                                                         | Vee <sub>t</sub> |                                                                                           | Transmitter Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                  | NA                 |

| 8                  | 13                                                         | TDis             | Optional use for<br>laser based<br>products only.                                         | Transmitter Disable: Optional Feature<br>Transmitter Output Disabled:<br>(Vcc <sub>t</sub> -1.3V) <v<vcc<sub>t<br/>Transmitter Output Enabled:<br/>Vee<sub>t</sub> <v< (vee<sub="">t+0.8V) or open circuit</v<></v<vcc<sub>                                                                                                                                                                                                | TTL                |

| 9                  | 14                                                         | TD+              |                                                                                           | Transmitter Data In<br>An internal 50 ohm termination will be provided for<br>gigabit/sec transceivers consisting of 100 ohm<br>resistor between the TD+ and the TD- pins. No<br>internal termination will be provided for lower speed<br>parts (622 Mb/s and below)                                                                                                                                                       | PECL               |

| 10                 | 15                                                         | TD-              |                                                                                           | Transmitter Data In Bar<br>See TD+ pin for terminations                                                                                                                                                                                                                                                                                                                                                                    | PECL               |

| No Pin             | 16                                                         | Veet             |                                                                                           | Transmitter Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                  | NA                 |

| No Pin             | 17                                                         | Bmon (-)         | If feature is not<br>used, do not<br>connect.                                             | Laser Diode Bias Current Monitor - Negative End:<br>Optional Feature<br>The laser bias current is accessible as a dc-voltage<br>by measuring the voltage developed across pins 17<br>and 18. Dividing the voltage by 10 ohms will yield<br>the value of the laser bias current. The stand-off<br>resistors should be 3k ohms. At an ambient of 25<br>degrees C, the voltage should range up to a<br>maximum of 0.70 volts. | NA                 |

| No Pin             | 18                                                         | Bmon (+)         | If feature is not<br>used, do not<br>connect.                                             | Laser Diode Bias Current Monitor - Positive End:<br>Optional Feature<br>See pin 17 description                                                                                                                                                                                                                                                                                                                             | NA                 |

| No Pin             | 19                                                         | Pmon(-)          | If feature is not<br>used, do not<br>connect.                                             | Laser Diode Optical Power Monitor - Negative End:<br>Optional Feature<br>The backface diode monitor current is accessible as<br>a voltage proportional to the photocurrent through a<br>200 ohm resistor between pins 19 and 20. The<br>stand-off resistors should be 3k ohms. At 50% duty<br>cycle, this voltage can range between 0.01 and 0.20<br>volts.                                                                | NA                 |

| No Pin             | 20                                                         | Pmon (+)         | If feature is not<br>used, do not<br>connect.                                             | Laser Diode Optical Power Monitor - Positive End:<br>Optional Feature<br>See Pin 19 description.                                                                                                                                                                                                                                                                                                                           | NA                 |